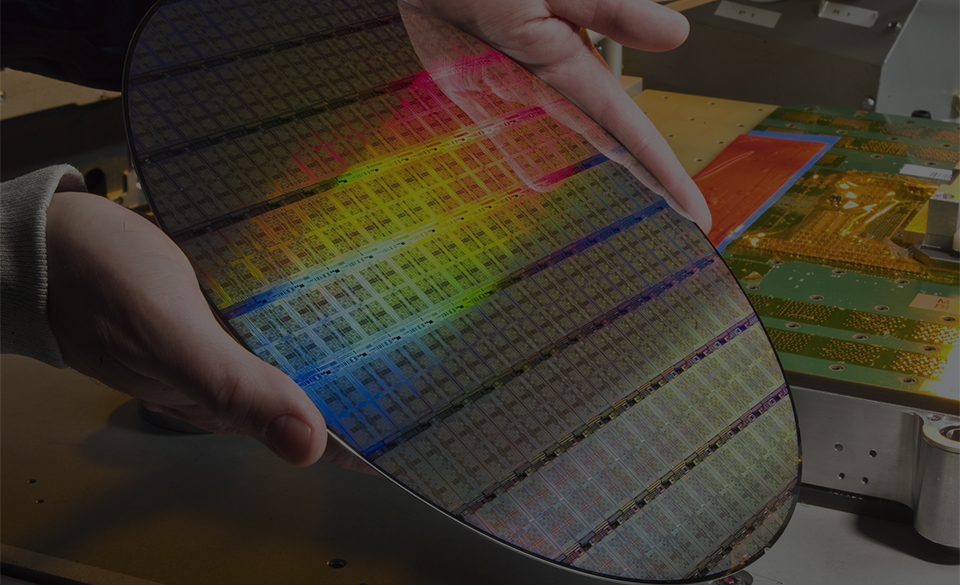

Công nghệ đúc wafer có thể mang lại những lợi thế nổi bật về hiệu suấtban ca sau, kích thước và chi phí tổng thể trong quá trình đóng gói bán dẫn. Với nhiều năm kinh nghiệm trong việc nghiên cứu và phát triển các hợp kim cũng như quy trình đúc wafer, bao gồm các phương pháp in với hợp kim eutectic, không chứa chì và hợp kim cột đồng, cũng như kỹ thuật tạo bóng hàn hoặc mạ điện. Hiện tại, sản phẩm đúc wafer cung cấp các giải pháp đóng gói chip flip-chip tiên tiến và đóng gói theo kích thước wafer với các kích cỡ wafer 200mm và 300mm, bao gồm đúc trực tiếp trên wafer, đúc với lớp trung chuyển và đúc dạng phân tán, nhằm đáp ứng mọi nhu cầu đa dạng của khách hàng trong ngành công nghiệp bán dẫn.

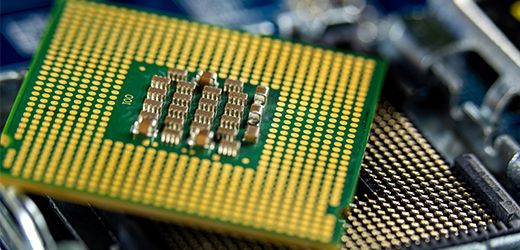

Trong công nghệ đóng gói chip flip-chipban ca sau, wafer được gắn trực tiếp lên nền bằng các bóng hàn thay vì sử dụng dây hàn. Điều này tạo ra sự kết nối dày đặc với băng thông cao hơn và tốc độ truyền dữ liệu nhanh hơn, đồng thời cải thiện hiệu suất điện tử và khả năng tản nhiệt. Các bóng hàn hoặc cột đồng được bố trí theo dạng lưới trên bề mặt hoạt động của thiết bị, có thể được đặt trực tiếp lên các pads đầu vào/đầu ra (I/O) hoặc dẫn tín hiệu từ các pads này. Công nghệ flip-chip chỉ thực sự hiệu quả khi các bóng hàn nằm chính xác trên các đơn vị điện tử mà chúng kết nối (bóng hàn I/O). Quá trình đóng gói chip flip-chip sử dụng vật liệu lấp đầy dưới đáy (CUF - Capillary Underfill) hoặc vật liệu đúc dưới đáy (MUF) trong không gian xung quanh các bóng hàn hoặc giữa bề mặt chip và bảng mạch để tạo ra cấu trúc đáng tin cậy và ổn định. Trong thị trường tiêu dùng, mạng, máy tính, di động và ô tô, công nghệ kết nối flip-chip là một phần quan trọng trong nhiều ứng dụng đa dạng.

Bao gói cấp wafer (WLP) có thể cung cấp hiệu suấtban ca sau, chức năng và tốc độ cao hơn trong các thiết bị nhỏ gọn, nhẹ nhàng và mỏng hơn. Bao gói cấp wafer tương tự như bao gói chip flip: cả hai đều sử dụng các bóng wafer để kết nối với bảng mạch. Kết nối chip flip thường sử dụng các bóng hàn nhỏ hơn, trong khi bao gói cấp wafer sử dụng các bóng hàn lớn hơn mà không cần vật liệu điền đầy. Nhiều bao gói cấp wafer sử dụng lớp tái tráng hóa dưới bóng hàn làm lớp đệm giảm lực cho mạch bên dưới. Về mặt chi phí-hiệu quả, có nhiều yếu tố linh hoạt có thể điều chỉnh trong quá trình tối ưu hóa thiết kế bao gói cấp wafer. Đây là một giải pháp thành công không chỉ áp dụng cho thị trường truyền thống như thiết bị di động và thiết bị cầm tay mà còn mở rộng sang các thị trường mới nổi như Internet vạn vật (IoT), thiết bị đeo và điện tử ô tô. Trong quá trình phát triển, bao gói cấp wafer không chỉ cải thiện hiệu suất mà còn tạo ra sự linh hoạt trong việc tích hợp các thành phần phức tạp vào các thiết bị nhỏ gọn hơn. Điều này đặc biệt quan trọng khi ngày càng nhiều người dùng mong muốn các sản phẩm có khả năng xử lý mạnh mẽ nhưng vẫn giữ được kích thước và trọng lượng tối thiểu. Với những ưu điểm vượt trội của mình, WLP đã và đang khẳng định vai trò quan trọng trong việc thúc đẩy sự đổi mới công nghệ trên toàn cầu.

Liên kết thân thiện:

Web cá độ bóng đá Nhà cái uy tín Web cá độ bóng đá Tỷ Lệ Kèo Nhà Cái 8XBET KBET Win88 Club